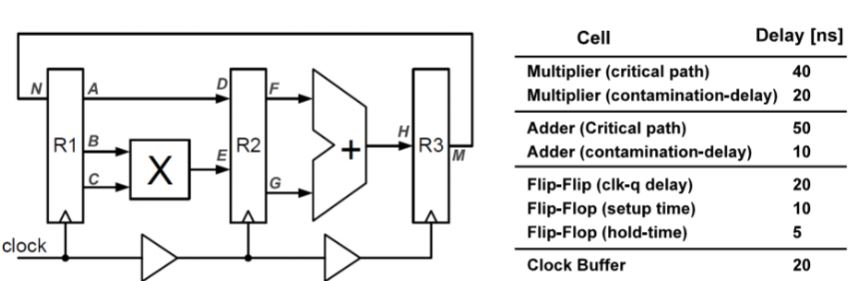

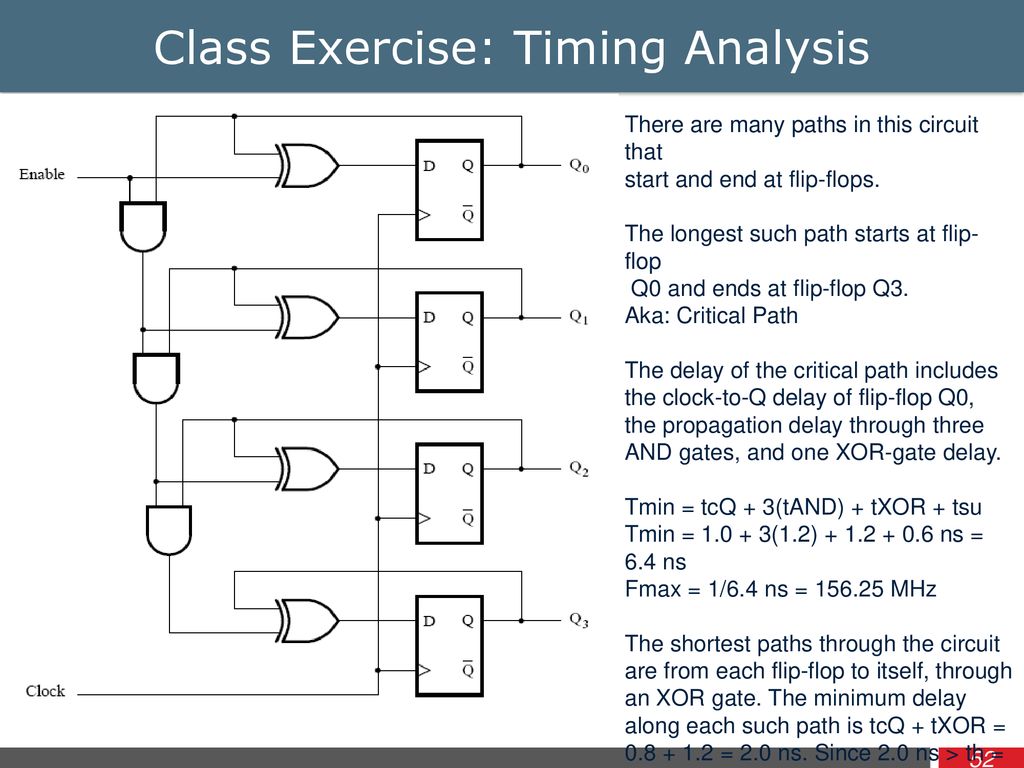

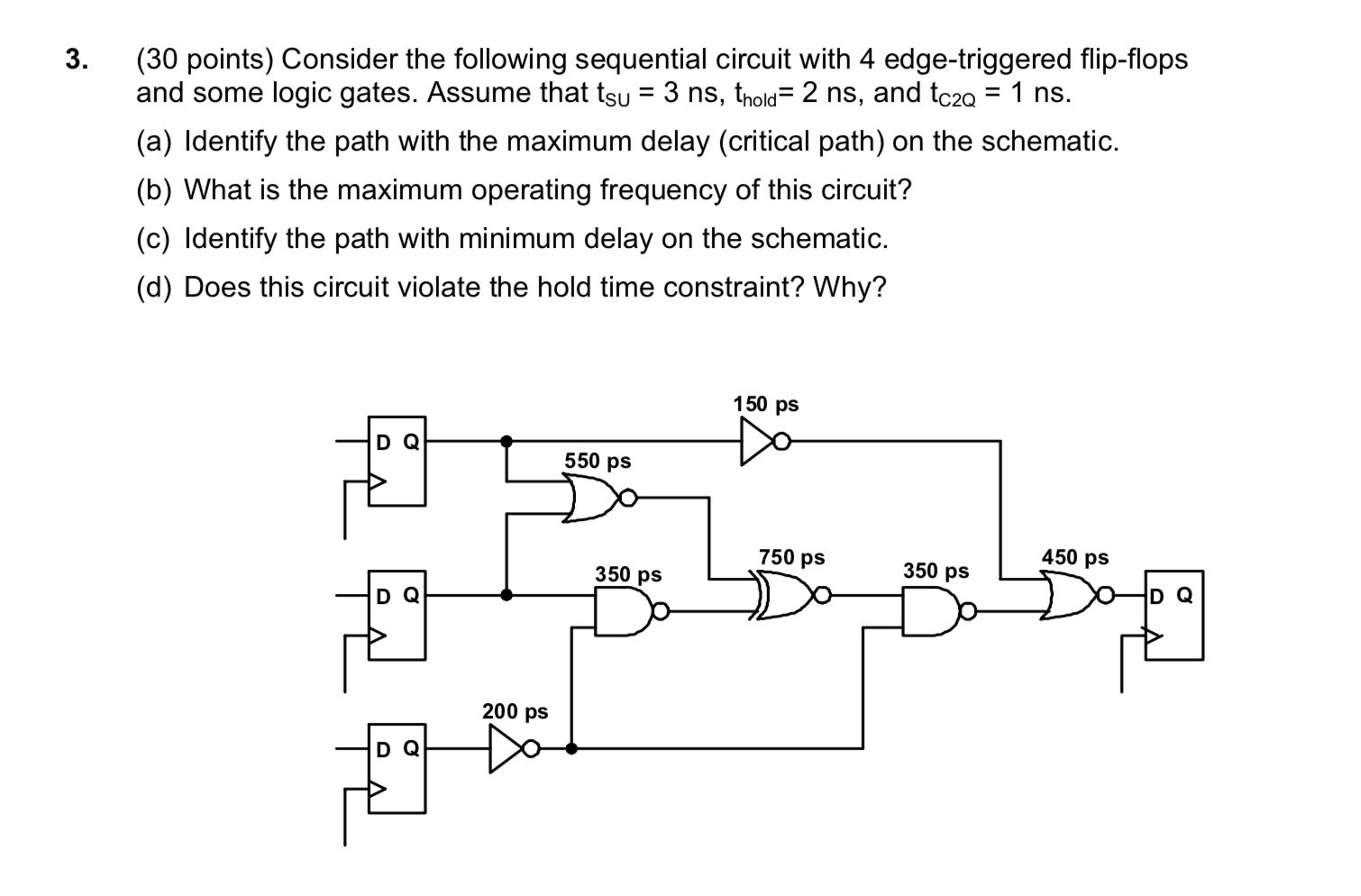

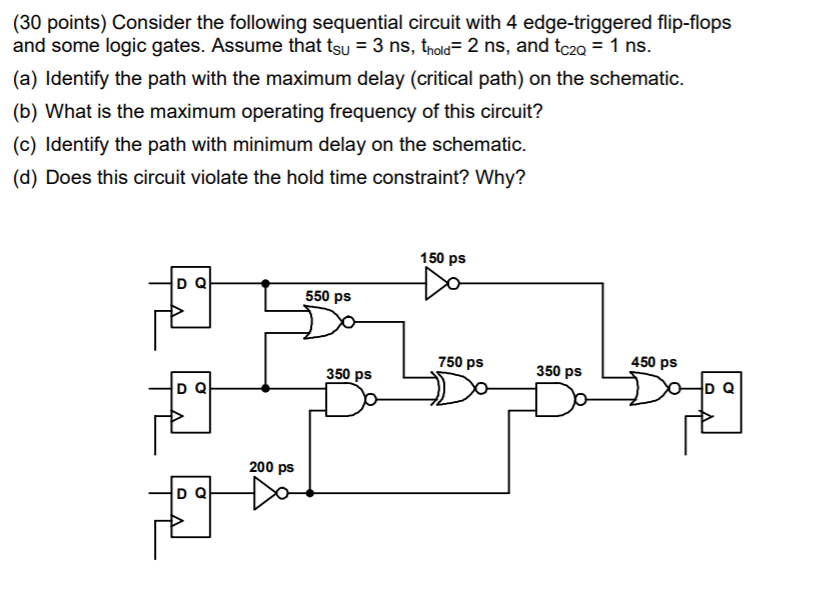

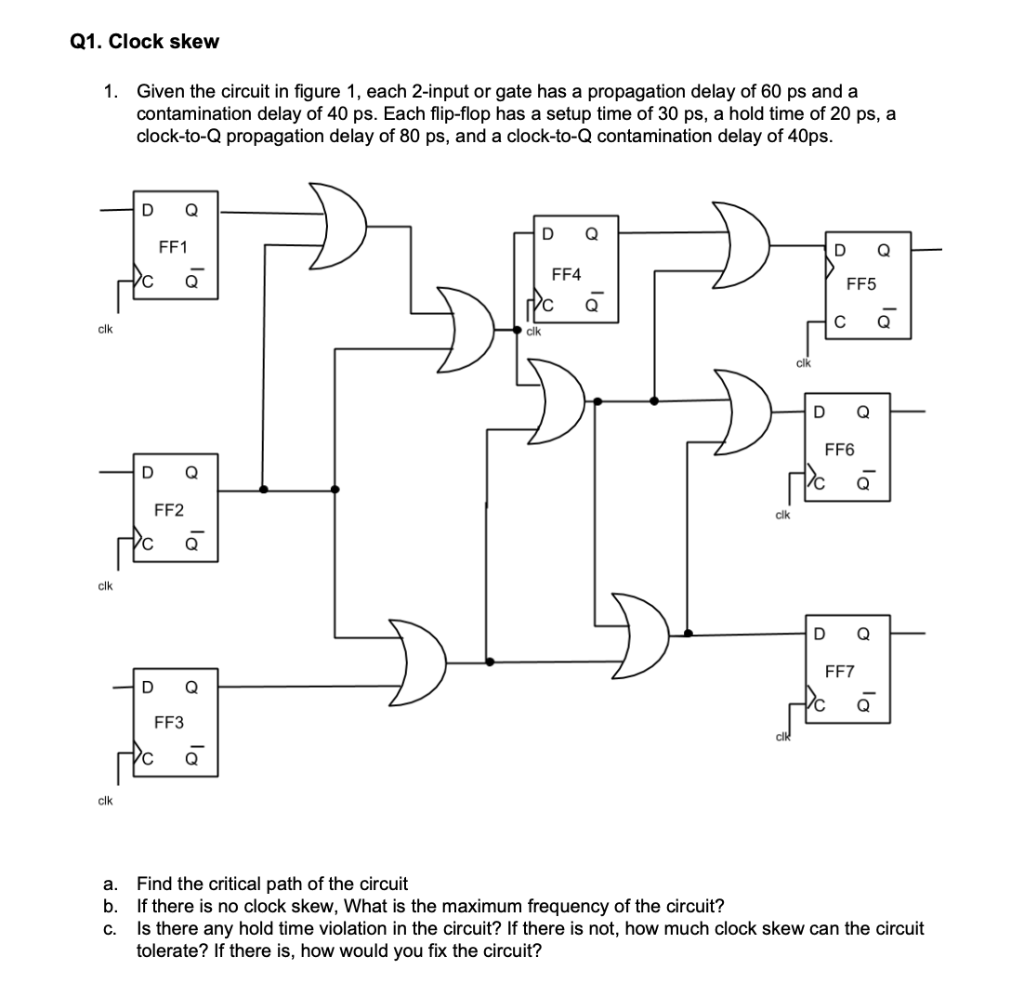

Xiao Patrick Dong Supervisor: Guy Lemieux. Goal: Reduce critical path shorter period Decrease dynamic power ppt download

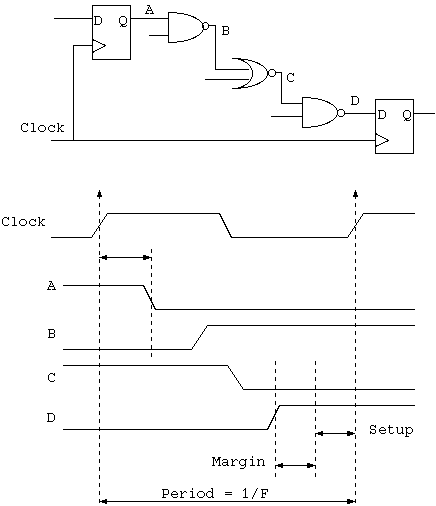

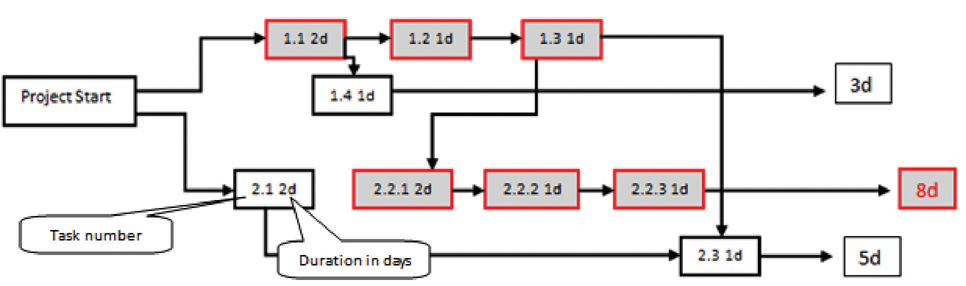

A previously proposed design for eliminating the performance penalty of... | Download Scientific Diagram

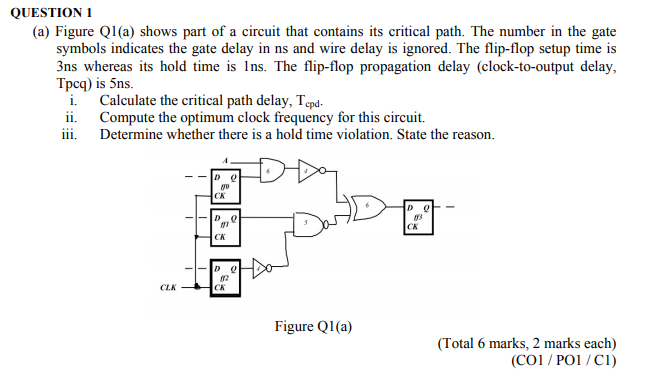

Figure 2 | A Modified Implementation of Tristate Inverter Based Static Master-Slave Flip-Flop with Improved Power-Delay-Area Product